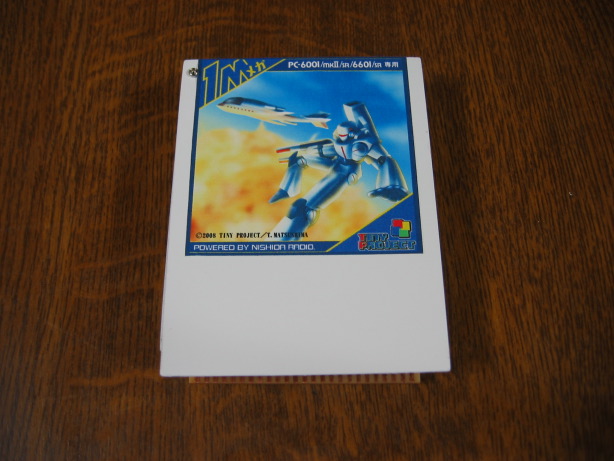

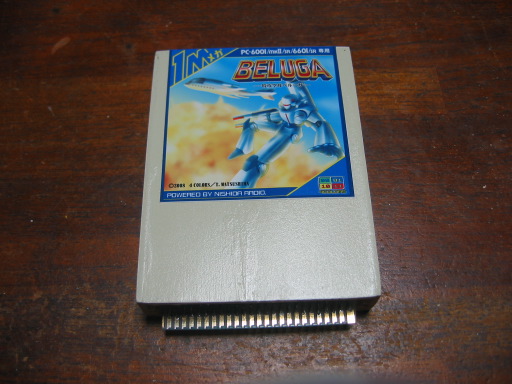

����͓ˑR�̏o�����ł����BHashi ����̃y�[�W�Ŕ��\���ꂽ�ABELUGA mkII �Ƃ����Q�[���BWindows �p�Ȃ̂ɁA��ʂ� P6 ���̂��̂� 4 �F�O���t�B�b�N�I��҂͂Ȃ�ƁAT.Matsushima ���I���킸�ƒm�ꂽ�A�`���̃v���O���}�[�B

���ɂƂ��Ă��AT.Matsushima ���̃^�C�j�[�[�r�E�X�A�^�C�j�[�[�r�E�X mkII �́A�ƂĂ��v���o�[���Q�[���ł��B�����AP6 ���[�U�[�Ŏ����Ă��Ȃ��l�͖w�ǂ��Ȃ������̂ł́H

����ȁA����� T.Matsushima �����A���x�� P6 �ŃQ�[��������Ă���ƌ����܂��B����͊��҂��Ȃ��킯�ɂ͍s���܂���I56K �o�C�g�̖c��ȃv���O�������A�J�Z�b�g�Ńs�[�K�[�b�ƃ��[�h����̂������ł����A����l�ɂ́A���ƃL�c�����i�j�H

����ŁA�J�Z�b�g�|���̃����J�[�g���b�W�ŗV�ׂ�l�ɂ��Ă݂܂��傤�A�Ƃ������b������A�����������͏o���Ȃ����ȁA�Ǝv��������ł���܂��B����[�A���N���N����Ȃ��i�j�B

�ԈႢ�̂���܂ܓ˂�����Ƃ����Ȃ��̂ŁA�����Ɏ��̐i���������čs�����ɂ��܂��B�F����̂������A��낵�����肢�������܂��B

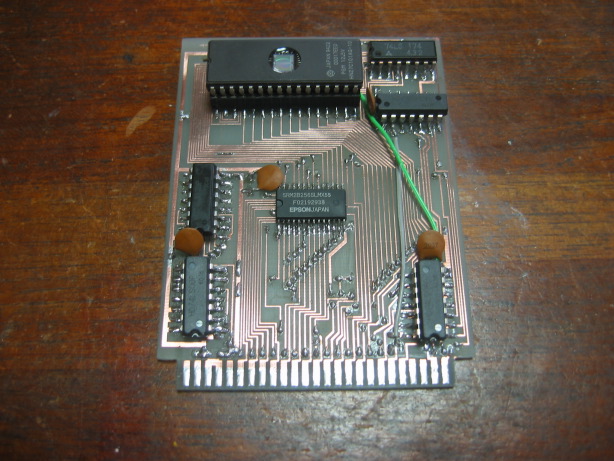

���炭�������Ă���܂����V���N�X�N���[������ɂ��v�����g����A�x���[�K�ɓK�p���Ă݂܂����B �悤�₭�A�x���[�K�̊���x�̔��ׂ��̃p�^�[���������o����l�ɂȂ����̂ł��B ����܂Ŋ�ɃR�X�g�������肷���Ă����̂ł����A����ŏ����y�ɂȂ�܂����B

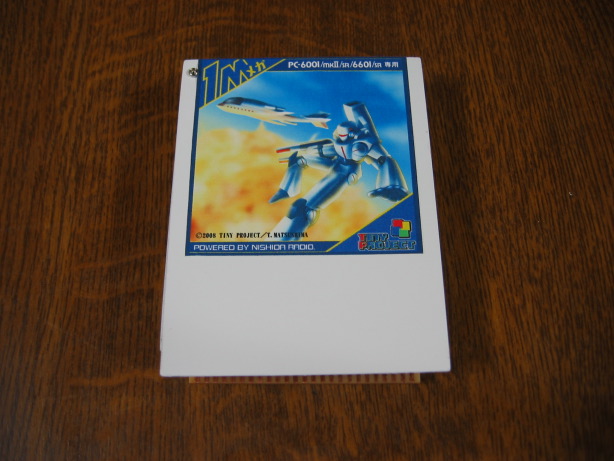

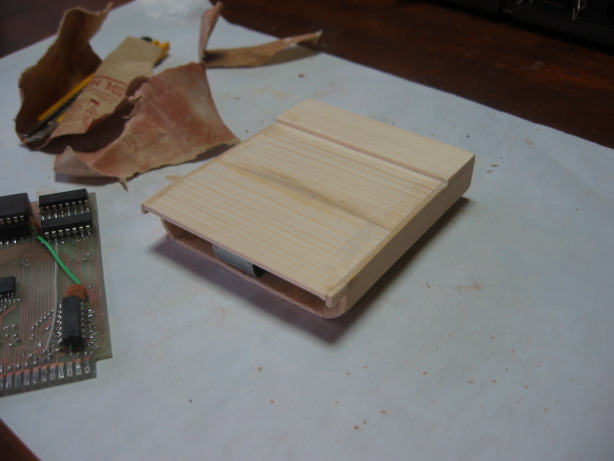

���ꂩ��A�P�[�X�̌^�����Ă��܂����̂ŁA��蒼���܂����B�`���܂łƈقȂ��Ă��܂��B

�܂��A�Ō��ɂȂ�^�����܂��BROM �̓����o�������Ă���̂ŁA�P�[�X�̒[���o�����点�Ă���܂��B

�،^�����ƂɁA���]�^�����܂��B�،^��K���Ȕ��ɓ���āA�V���R���S���𗬂�����č��܂��B

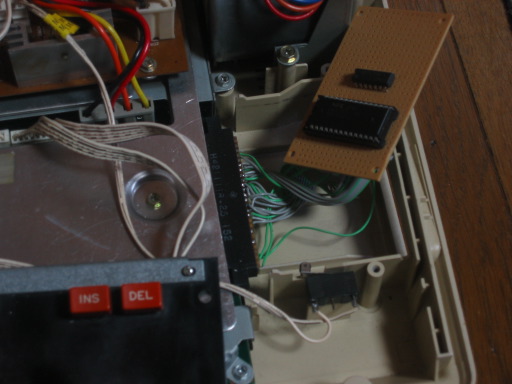

��O�́A�e�X�g�p�ɗ����Ă݂������ł��B

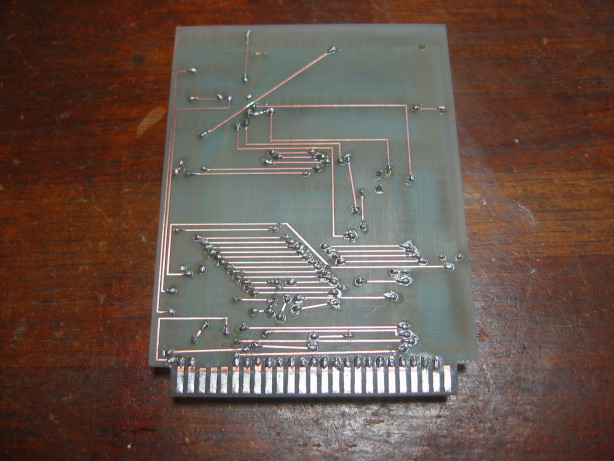

���]�^�Ɏ����𗬂�����Đ��`���܂��B�E���^�������ɔ��A�h�~�܂����Ă���܂��B

���^�����߂ɁA�������AROM �����J���܂��B���R�͌�q�B

�v���łŔw�\��������ă{���h�œ\��A�\�ʂ𐮂��ēh�����ďo���オ��B ���̂悤�� ROM ���ォ�獷�����ގ��ɂ��A�����Ɋ���Œ肳���d�g�݂ł��B

���͂���Ȋ��������x����\�����Ƃ���B

��̐��`�ł͂���܂��A����ł��ؐ��̃P�[�X���͗y���ɋ��x������܂��B

���̊��ɋy��ŁA���ʃv�����g��ɒ��킵�܂����B ���Ɨ������X������܂������A�悤�₭�ꖇ�o���܂����B �m�E�n�E�͑�R���肷���ď����܂���B

�����ڂ͊��ł��B �K���X�G�|�L�V�ł��邱�ƁA�[�q������̉��������ƂŁA ���x�͂��Ȃ葝���Ă��܂��B �O��肸���Ɖ��ɂ����Ǝv���܂��B ���E�܂ŃR���p�N�V�������āA�������^�ɂȂ��Ă��܂��B

�������̂͑��ς�炸��ςł��B IC ���O������t������A���Ȃ莎�s���낵�܂����B �o�O�͑S�āA�p�^�[���̃~�N���̃u���b�W����ł����B ����Ȃ̂Ŋ����͕s�\�ł��B

�R�X�g�A�b�v�� 700 �~�قǁi��̎��s�����l�����āj�A�����͂Ȃ��ł��B �ł��A�L�� P6 �� ROM �J�[�g���b�W�Ƃ��Ďg�p�ł���Ǝv���܂��B

��H��ύX���܂����B

http://www7b.biglobe.ne.jp/~tulip-house/digital/BELUGA/

6000-7FFF �� RAM1 �̕����̃��C�g�v���e�N�g���o����悤�ɂ��܂����B����́AmkII �ȍ~�Ŏg�p���ɁA���� RAM �ƓƗ����� RAM1 ���g����l�ɂ��邽�߂ł��BSD �J�[�h���[�_�̏����̊g���̂��߂̃n�[�h�ύX�ł��B

�Ƃ��낪�B�B�B

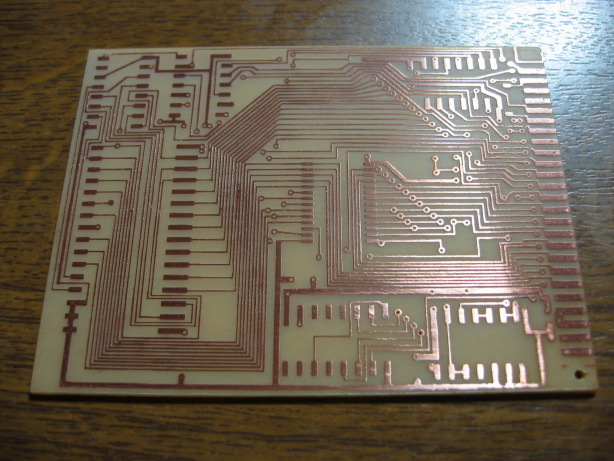

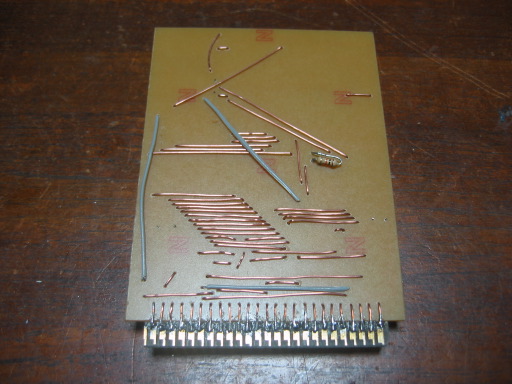

����܂ł̃J�[�g���b�W�W���A�p�^�[���J�b�g���z���Ń����[�N�����̂ł����A���ꂪ���ʒ���ςł����B�����āA���̂W�̌��_�����炩�ɂȂ�܂����B

�ŏ��̂V�́A�v�����g��̗��ʂ� 0.55 mm �̌ł߂̓����Ŕz�����Ă���̂ł����A�v�����g��̃p�^�[�����ׂ������߁A�������Ă���ƃp�^�[������ă����h�������Ă��܂��̂ł��B���������̌��ׂ́A�����ڂł͂قƂ�ǂ킩��Ȃ��̂ŁA��������̂���ςȂ̂ł��B�B�B�ˑR�����Ȃ��Ȃ��āA�������킩��Ȃ��ēr���ɕ��Ă��܂��������Ȃ�̕p�x�ł������̂ł��B

�I�[�N�V�����p�̂P�́A0.28 mm �̏_�炩���������Q�{�p���ɂ��Ĕz�����Ă���̂ł����A�z�����y�Ȃ����ł͂Ȃ��A���̂悤�ȃ����h�������N����ɂ����Ƃ������������邱�Ƃ��킩��܂����B�c�O�Ȃ̂́A�J�[�g���b�W�̒[�q�ւ̔z�������ł��������g���Ă��邱�Ƃł��B���K�i�͑S�� 0.28 mm �̓����ōs�����ɂ��܂��B

�ŏ��̂V�͊W�җp�̃J�[�g���b�W�ł����A���� ROM �̔������������ĐF�X���p���悤�ƌ������́A�ł���ΐ��K�i���ĉ������B���K�i�̕����y���ɉ��ɂ����Ȃ肻���ł��B

�x���[�K�̃J�[�g���b�W�� HP �����܂����B�܂������ɂ͔���J�ł��B

markn ����� Joystick-SD �J�[�h�A�_�v�^�̃u�[�g���[�_�� ROM �ɔE���鎖�ɂȂ�܂����B

�������Amarkn ���撣���č���Ă���Ă��܂��B

http://www7b.biglobe.ne.jp/~tulip-house/digital/BELUGA/

�g�����Ȃ��Ă��܂����ˁB�F����A���������߂����ł��傤���H

���́A�悤�₭�~������o�߁A�̂������������l�ɂȂ�܂����B

���āA�i���ł����A�J�[�g���b�W�̃n�[�h�͂V��o���Ă��܂��B

���̂����A�o���̈������̓��^�N�V�p�Ȃ̂ŁA�U��ł����B

�����A�v���O�����̕����܂� fix ���Ă��Ȃ��̂ŁA�e�X�g�p�ȊO�� ROM �͏Ă��Ă��܂���B

���ꂩ��ABeluga �̂��߂����ł͂Ȃ��̂ł����AUSB �ڑ��Ŏ�y�Ɋe�� ROM ���Ă��� ROM ���C�^�����܂����B

����͐��c���a�I���甭���\��ł��i����������`�j�B

���C�ɂȂ��Ă����̂ŁA�悤�₭��ƍĊJ�I

�����̓v�����g����S�����܂����B�ꖇ���ɁA��肭�Ȃ�܂��B

�ŏ��̍��͏C�����炯�̊�ł������A���͏C�������Ȃ��Ȃ�܂����B

����ł��[���ɂ���̂͂Ȃ��Ȃ�����̂ł��B

�C�����炯�̊�ɓ����������́A���߂�Ȃ����i�j�B

�P�[�X�͖ؐ��ł��B�ׂ����q�����킹�Ă���̂ŁA���܂����������܂���B�F�̓A�C�{���[�ł��B

���̃l�W���O���ƁA������o���܂��BROM �̍����ւ����ł��܂��B

�h���͂��܂�������Ȃ����ǁA����Ȃ̂ł��̂��炢�ł����ق��B�B�B

�]�ɂ̂قƂ�ǂ��x���[�K�ɂ�����ł��܂��A���^�N�V�B�B�B

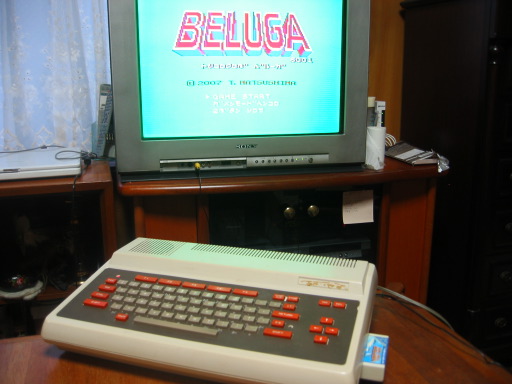

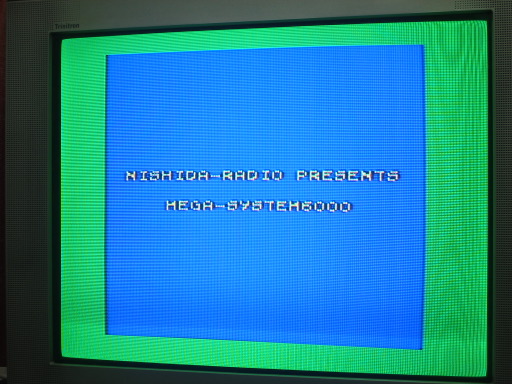

���āA�J�[�g���b�W�ł̎���o�C�i���ɁAT.Matsushima ���������d�|�������Ă���܂����BNISHIDA RADIO PRESENTS MEGA-SYSTEM6000 �����āI���肪�Ƃ��AT.Matsushima ����I

�\�t�g�̌��� ��݂��� ����ɔC�����A�Ǝv���ăn���_�t�����Ă���Ώ����܂����B�B�B�\�t�g�������ƌ���Ƃ������H�Ƃ����킯�ŁA�\�t�g���������Ă݂܂����B

�L���������̌����́A�e�[�v�łƃJ�[�g���b�W�łł́A�L�����̊i�[�A�h���X���Ⴄ���炾�Ǝv���܂��Bz80vdp60 �� set_rom_cg12 / cg1 / cg2 ���ŁASET 6,D; RES 5,D ��lj����ĕ���Ă��Ɖ����Ȃ��Ȃ�܂��B

�^�C�g���� (C) ��������̂ł����A�������R�ł��Bz80ma60 �� call set_rom_cg2 ���ALD B,8 �̌�Ɉړ�����ƒ���܂��B

set_rom_32 ���̃������ݒ�́ALD A,71H �̂܂܂� OK �ł��B

���ƁA��ʂ̍��E�̒[�ɃS�~���c��܂��B����͂悭�킩��Ȃ������ł��Bz80eshot �� check_eshot_maphit �� CP 2 �� CP 4 �ɂ����肷��ƁA���[��������܂��B�B�B

�Ƃ���Ń��^�N�V�� Mac ���[�U�Ȃ̂ŁA�ăr���h����������ł��i�܁j�B���Ԃ�T���ăR�[�h���l�ߍ���Ŏ������Ă܂����i�j�B

�����̓n�[�h�̕��ł��i��������܂����B���� mkII �ł́ARAM �͑S�Ė{�̓��̂��̂��g�����Ǝv���Ă����̂ł����A���ƁA�{�̓��� RAM �� 16 �L���o�C�g�P�ʂł����A�T�C���ł��Ȃ��̂ł��B�B�B�܂�A4000-5FFF �� ROM �ŁA6000-7FFF �� RAM�A�Ƃ����킯�ɂ͂����Ȃ��̂ł��B�d���Ȃ��n�[�h�������������AmkII �ł́A6000 - 7FFF �������J�[�g���b�W�� SRAM �ɂ��邱�Ƃɂ��܂����BSRAM �� OE �ɁADRD �� RD �� or �������Ă��܂����A����� DRD �� CS3 �� or �ɂ��܂��B�����ăX�C�b�`����������ăV���[�g�����Ă��܂��܂��B����ŁA�X�C�b�`��ւ��Ȃ��ŁA����@�� mkII �ȍ~�ŋ��p�ł���̂ł��B�܂�AmkII �ł́ARAS and EXCAS �́A�i�O��RAM���g��Ȃ��Ȃ�j��ɃC���A�N�e�B�u�ł��B������ CS3 �́A�Ή�����O�� ROM �̃��[�h���݂̂ɃA�N�e�B�u�ɂȂ�܂��B���̐M���́A��݂��낳��ɒ��ׂĒ������悤�ɁA�A�h���X�f�R�[�h���ʂƃ��������[�h�M���������Ă��܂�����A����� SRAM �� OE �ɓ˂����߂A�����̃������ƂԂ���S�z�����Ȃ��Ă������̂ł��BmkII �ł́ADRD ����ɃC���A�N�e�B�u�ł��B�����āA6000 - 7FFF �ɏ������݂�����ƁA��� SRAM �ɏ�����܂��B�����ɓ��� RAM �ɂ��������ł��傤�B

mkII �ł��J�Z�b�g�|���o���܂����I�����A�̂� ���������������Ă���悤�ɁA�������M�N�V���N���܂��B����@�͌��\���炩�ɓ����̂ł����B�B�B

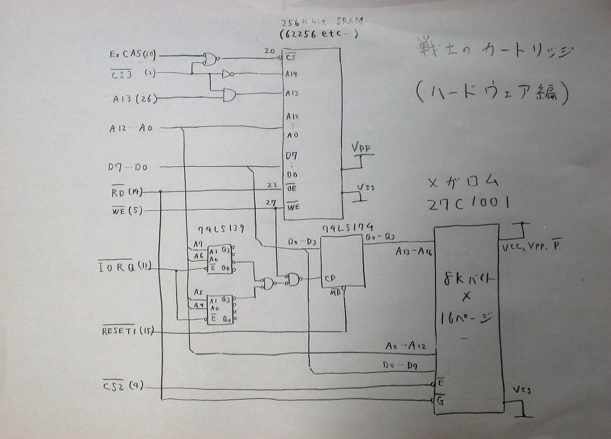

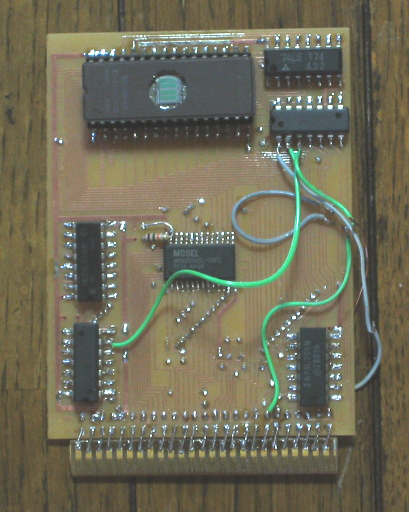

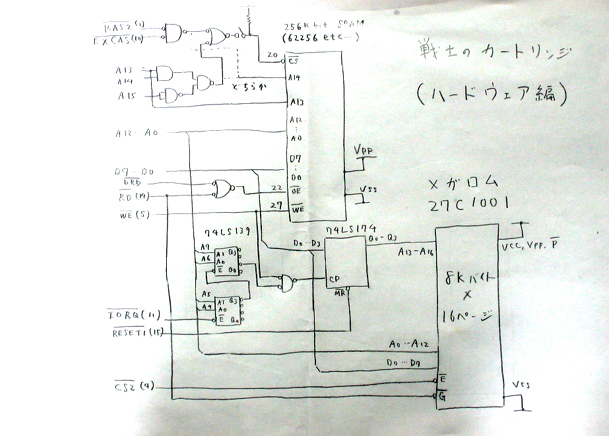

�܂��́A��������B���ǁA�Z�p�I�Ȗ���R�X�g�ʂ��l���A�Жʃv�����g��ł�邱�Ƃɂ��܂����B�^�̏������`�b�v�� 256K �r�b�g�� SRAM�A��̑傫���`�b�v�����K���� (1M �r�b�g) �ł��B

�Ă����f�[�^�́AT.Matsushima ����� ROM �ł̃f�[�^��w�ǂ��̂܂g���Ă��܂��B��_�����C�����Ă��܂��B�ŏ��̃v���O�����]���� (LDIR) �Ɋ��荞�݂��֎~���܂����B

�����āA���悢��N���I���A���������I�ł��A�L�������o�P�o�P���B�B�B

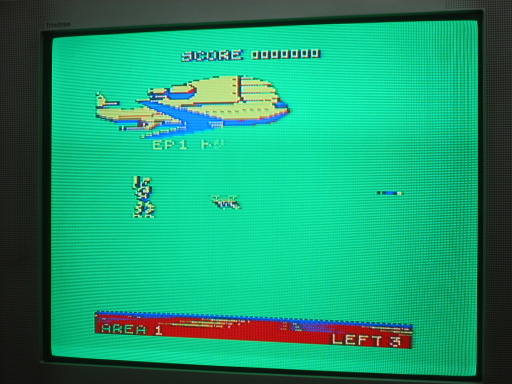

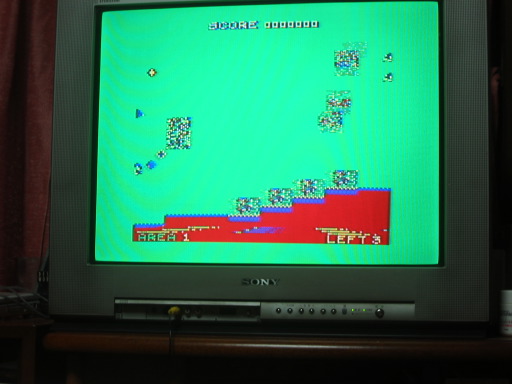

�Q�[���͕��ʂɂł���悤�ł��I�X�N���[���S�� OK�B

�C�ɂȂ����_�́A��≹���c�ނ��Ƃł��傤���H�G�~���ł́A���ɖ��Ă���̂ł����B

�L���������́A�b��I�Ƀ��K�����ɑΉ������G�~�� (Cocoa iP6) �ł��A�����l�ɔ������܂��B

�܂��ASRAM ���I�t�ɂ��Ă��AmkII �ł͓����Ȃ��悤�ł��B

�\�[�X���������Ă���̂ł����A�L���������̌������悭�킩��܂���B�v���O���������x�����āi�j�B�B�B �G�~���J���҂̕��ŁA���K�����Ή�����邩���́A���������ɂ����͒�����Ɗ������ł��B

���ꂩ��A�S�R�W�Ȃ��b�ł����A�X�[�t�@�~�{�̂��J���������ȃh���C�o�[���������̕��A���݂�������Ί������ł��BSRAM ���X�[�t�@�~������̂Łi�j�B�܂��A�t���b�g�p�b�P�[�W�� 256K �� SRAM ���������̕��A�����蒸����ƗL���ł��B�W�����N�ł����ł��\���܂���B

��ꍆ���삵�܂����i�L�^�i�N�Ă��݂܂���j�B�Ƃ肠�����A�ȒP�ȃe�X�g�ł͐����������Ă���悤�ł��B

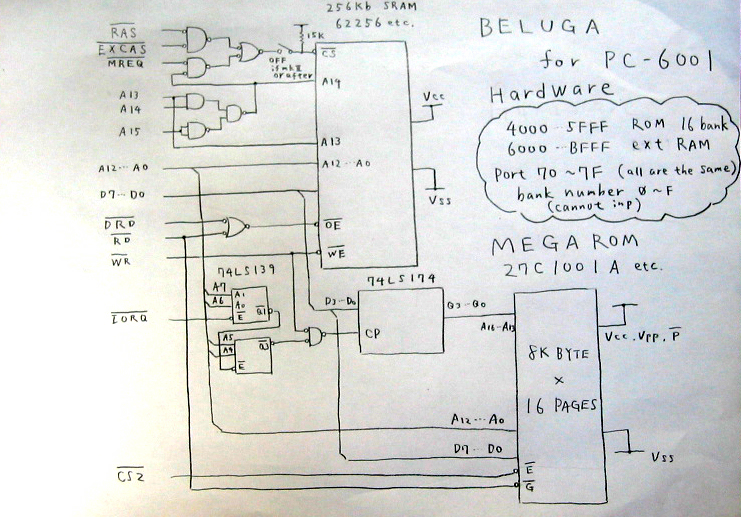

�ŏI�I�ȉ�H�́A�ȉ��̗l�ɂȂ�܂����B�ȒP�Ȏd�l�������Ă���܂��B�e�G�~�����[�^��҂���͎Q�l�ɂ��Ă��������BT.Matsushima ���G�~���Ńe�X�g�o����悤�ɑΉ����Ē�����Ɗ������ł��B

����̃v�����g��́A���c���a�I�I�ɂ͌��E�ɋ߂��i�j���ׂ��Ȃ̂ŁA�S�z���Ă��܂������A�Ȃ�Ƃ���肭�o�������ł��B�P�[�X�́A�̔����ƃv���X�`�b�N�łō�낤�Ǝv���Ă��܂��B�ȑO������AROM / RAM �J�[�g���b�W�̒Z���ł̂悤�ɂȂ�͂��ł����B���x���͓V�ۂ���ł����H�H�H

�Ō�ɁA�F����ɂ��肢�ł��B�����m�̕��������Ǝv���܂����A�l�͐��_�̕a�C�������Ă���̂ŁA�ˑR�����ł��Ȃ��Ȃ�A�R�����炢�Q���肷�邱�Ƃ�����܂��B���̂��߁A�[������������Ȃ����Ƃ������ł����A�����A������������悤�A���肢�������܂��B

��݂��낳��A�d�v�Ȏ��������w�E�����܂����B���肪�Ƃ��������܂��I

�yCS3��READ���̂ݗL���z

�Ȃ�قǁ`�B�������A�d���Ȃ��̂ŁA�A�h���X���f�R�[�h���ASRAM �̃`�b�v�C�l�[�u�������܂����B��������� mkII �ȍ~�ŐM�����Ԃ���̂ŁAmkII �ȍ~�ł̓W�����p�[����ύX���鎖�ɂ��܂����B

�yCAS�͓���RAM�ƊO��RAM�ŋ��p���Ă���z

��݂��낳��̂��w�E�ǂ���ɁARAS �� CAS �� AND �i���_���j���g���l�ɂ��܂����B

���̑��ASRAM �� OE ���ADRD �� RD �� OR�i���_���j�ɒ������܂����B

�Q�[�g���팸�̂��߁AIO �|�[�g�A�h���X�̃f�R�[�_ 74LS139 ���V���A���ɐڑ����܂����B

����ŁASRAM�A���K ROM �̑��ɁATTL �� 5 �ɂȂ�܂����B��̃T�C�Y�� 75mm x 100 mm �ɂȂ�Ƃ����߂Ă܂����A�����ɂ��Ă͂��Ȃ�ׂ����p�^�[���ɂȂ��Ă��܂��܂����B�I���������ɂ��Ȃ���Ȃ�Ȃ��ł��傤�B

��݂��낳��A���肪�Ƃ��������܂����B

�ȉ����AT.Matsushima ���̗v���d�l�ł��B

0000h-2000h basic rom only �m������@�͂����Ƀo���N�������H

2000h-4000h basic rom only ����

-----------------------------

4000h-6000h extend bank rom �W�j�~�U�o���N����ΑS�����܂��B

6000h-8000h extend ram �������q�`�l�ł��鎖���K�{�B�������L�c�C�B

8000h-a000h extend ram �g���q�`�l�P�U�j�a

a000h-c000h extend ram ����

-----------------------------

c000h-e000h main ram �����q�`�l�P�U�j�a

e000h-ffffh main ram ����

�v�́APC-6006 ���l�� 16KB �� RAM �ɉ����A8KB (4000-5FFF) �� ROM1 ���o���N�ؑւ� 6 �y�[�W�p�ӁA ����� 8KB �� ROM2 �̋�� (6000-7FFF) �� RAM �ɂ���A�Ƃ̎��ł��B

���U�@�ōs���A16KB �� RAM �� DRAM �ŁA8KB �� RAM �� SRAM �ŁA�ƂȂ�̂ł��傤���A��� RAM ���ڂ���̂́A���傢�Ɩ��ʂ̂悤�ȋC�����܂��B

P6 �ł́A�O�t���̃������� DRAM ���g���l�ɐv����Ă��܂��B�ł������ SRAM �ŏo����Γs�����ǂ��ł��B�����AP6 �� SRAM ���q��������������A��������q����܂��ˁi�j�B

�A�h���X���f�R�[�h���ă`�b�v�C�l�[�u���M�������̂��{���ł����A��������� mkII �ɃJ�[�g���b�W��˂������ɁA�{�̓��� RAM �ƐM�����Ԃ����Ă��܂��܂��B�K���ADRAM �p�� RAS / CAS �M�����A���ȏ��ʂ�̐M���̂悤�Ȃ̂ŁA��������̂܂܃`�b�v�C�l�[�u���ɂ��Ă����삷��悤�ł��B RAS �� DRAM ���t���b�V���ł��A�N�e�B�u�ɂȂ�̂� CAS ���g���܂������A�ǂ���ł����Ȃ����삵�܂����B�A�h���X�f�R�[�h��H���s�v�ł��B

�Ƃ����킯�ŁA��H���l���Ă݂܂����B ���āA�����������̂ł��傤���H